Giải pháp Napatech, Tin tức Napatech

Nâng cấp Suricata lên tới tốc độ 100Gbps với Napatech SmartNICs

Nâng cấp Suricata với Napatech SmartNICs

Tăng tốc hiệu năng của Suricata lên tới 100 Gbps với Napatech SmartNICs sử dụng công nghệ xử lý stateful flow.

Link-25, 2-port 25 gigabit Ethernet SmartNIC

Link-100, 2-port 100 gigabit Ethernet SmartNIC

Tăng tốc Suricata với công nghệ xử lý Napatech stateful flow

Suricata là bộ phần mềm engine phát hiện nguy cơ an ninh mạng (threat detection engine) nguồn mở, hoàn thiện, hoạt động nhanh và mạnh mẽ. Suricata engine phù hợp với ứng dụng IDS (intrusion detection) thời gian thực, IPS (inline intrusion prevention), NSM (network security monitoring) và bộ xử lý offline PCAP. Suricata sẽ rà soát toàn bộ traffic của mạng sử dụng các bộ rule mạnh mẽ, mở rộng và khả năng hỗ trợ Lua scripting cho việc phát hiện những nguy cơ tiềm ẩn và phức tạp. Nếu một nguy cơ hoặc một hành động bất thường nào bị phát hiện, Suricata sẽ gửi cảnh báo tới quản trị viên và ngay lập tức khóa hoặc tạm dừng nguy cơ đó.

Việc tăng lên nhanh chóng của traffic và sự gia tăng mức độ phức tạp của các cuộc tấn công đang đặt CPU của thiết bị IPS/IDS phải hoạt động hết công suất để chống đỡ. Một trong những phương án hữu hiệu để giải tỏa sức nặng cho CPU của các thiết bị này là chia sẻ khối lượng công việc xử lý tập tin từ CPU sang một thiết bị FPGA-based SmartNIC.

Napatech SmartNICs đã chứng tỏ được khả năng bảo toàn vẹn dữ liệu đi qua Suricata bằng việc cung cấp tính năng zero-copy DMA (Direct Memory Access) của gói tin đi từ NIC tới ứng dụng, giải phóng khối lượng công việc của CPU cho vấn đề này.

Phiên bản mới nhất của Suricata có thể được tăng tốc mạnh mẽ hơn bằng việc sử dụng Napatech SmartNIC để xử lý những khối lượng công việc quan trọng trong việc xử lý gói tin trong FPGA trên nguyên lý mỗi luồng mà không cần xử lý traffic trên CPU.

Tăng tốc Suricata

Để đánh giá mỗi gói tin theo thời gian thực để phát hiện ra hàng ngàn các cuộc tấn công trên hàng trăm hay hàng ngàn luồng dữ liệu đồng thời đòi hỏi máy tính có một năng lực tính toán cực kì mạnh mẽ. Để giải quyết vấn đề này, kể từ phiên bản Suricata 3.2 đã cho phép quản trị viên lựa chọn những traffic cụ thể theo từng tiêu chí và có thể loại bỏ khỏi luồng xử lý một khi xác định đó là dữ liệu an toàn. Đây chính là sự tối ưu cho phép dữ liệu được đi qua bộ phân tích gói tin khi việc dự đoán gói tin là an toàn.

- Những tình huống cho phép gói tin đi qua thường được áp dụng:

- Traffice được mã hóa: Ứng dụng Suricata sẽ bỏ qua khâu xử lý các dữ liệu được mã hóa như TLS, IPsec, Kerberos sau khi có sự thỏa hiệp về dữ liệu

- Dịch vụ streaming: khi một lượng lớn dữ liệu được gửi đi từ những nguồn đã biết như nhạc, phim từ Netfilx, Youtube, Spotify, Apple Music, luồng dữ liệu này sẽ được đi qua hoặc bị chặn lại theo như cấu hình của quản trị viên mà không cần phải xử lý từng gói tin riêng biệt

- Những trường hợp đặc biệt theo dạng đặc biệt của dữ liệu: những luồng dữ liệu lớn khác như dữ liệu backup đi đến từ những địa chỉ host hay ứng dụng đã được tin cậy

Nâng cao năng lực của Suricata với Napatech SmartNIC

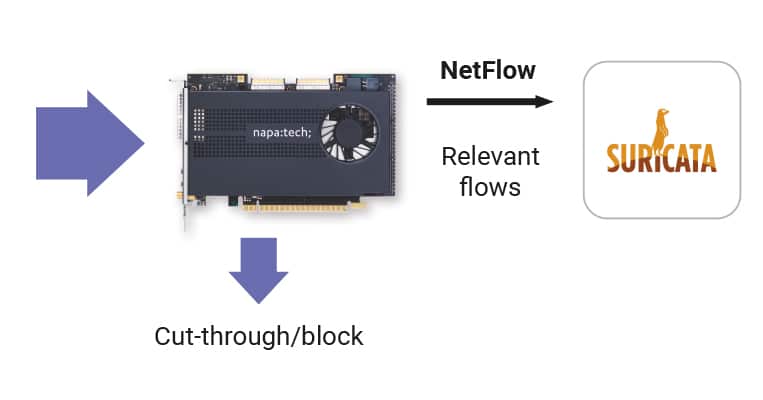

Những thiết bị mạng hay ứng dụng an ninh như Suricata sử dụng rất nhiều tài nguyên CPU để xử lý dữ liệu nhưng không phải tất cả các gói tin đều cần phải được xử lý. Chỉ một vài gói tin đầu tiên trong một luồng dữ liệu có thể có ích hoặc những giao thức cụ thể có thể bị bỏ qua hay chỉ những gói tin tới/từ một địa chỉ cụ thể mới cần phải kiểm tra. Giải pháp của Napatech sử dụng cơ chế xử lý dựa trên luồng dữ liệu để bỏ qua x86 altogether (FWD, block, redirect) bằng một cơ chế work-load-specific FPGA cho xử lý luồng dữ liệu. Điều này yêu cầu những sự phối hợp chặt chẽ giữ các ứng dụng x86 và SmartNICs thông qua các hàm APIs cho phép ứng dụng có thể thay đổi các hành động dựa trên từng luồng dữ liệu.

Ý tưởng cơ bản của việc bở qua này là dừng việc xử lý gói tin mà không cần phải kiểm tra thêm nữa trong một chu trình xử lý gói tin. Tính năng này được kích hoạt trong Suricata bằng từ khóa ‘bypass’ trong các cấu hình rule, điều này rất đáng kể khi một kết luận được đưa ra, mọi traffic khác trong cùng một luồng dữ liệu có thể được bỏ qua việc decode và kiểm tra để giảm thiểu việc tiêu tốn năng lực phần cứng.

Ví dụ, đây là một câu lệnh để bỏ qua những luồng dữ liệu tương ứng với địa chỉ IP address:

pass ip 1.2.3.4 any <> any any (msg:”pass all traffic from/to 1.2.3.4”; bypass; sid:1;)

Napatech mở rộng khả năng này bằng cách cho phép phần cứng SmartNIC xử lý các dữ liệu đã được bỏ qua trên FPGA mà không cần sự tham gia của Suricata hay của CPU. Khi không có Napatech FPGA-based SmartNIC, câu lệnh này sẽ được xử lý trong phần mềm. Khi Napatech SmartNIC được sử dụng, hành động bỏ qua này sẽ được thực hiện trên programmable SmartNIC, điều này làm tăng hiệu năng và giảm khối lượng xử lý cho những vi xử lý thông thường.

Sự hỗ trợ cho tính năng này đã được phát hành trên Suricata git repository bởi Open Information Security Foundation (OISF) và sẽ được tích hợp vào phiên bản mới của Suricata.

Việc triển khai được dựa trên Napatech Flow Management API cho phép một ứng dụng có thể theo dõi traffice trên mỗi luồng dữ liệu để giải phóng một số hoặc toàn bộ khối lượng công việc xử lý trên SmartNIC FPGA: việc phân tích mức ứng dụng vẫn được giữ nguyên trên CPU trong khi trên mỗi gói tin hành động xử lý sẽ được thực thi trên phần cứng của network interface card.

Flow Management API cho phép quản lý luồng dữ liệu qua chu trình khép kín:

- Duy trì bảng các luồng dữ liệu đang hoạt động

- Thêm vào các luồng mới

- Thực thi hành động trên từng gói tin

- Đồng bộ bộ đếm gói tin/byte

- Cập nhật các bản ghi luồng dữ liệu khi bị ngắt hoặc timeout

Mã nguồn của Suricata cung cấp một mẫu code cho việc tích hợp Napatech API cho các lập trình viên hoặc cho các ứng dụng khác.

Với việc tích hợp chức năng Napatech Flow Manager vào phần mềm, người sử dụng Suricata không cần phải lập trình hay chỉnh sửa mã nguồn: tính năng này có thể được truy cập thông qua các giao diện thanah thiện trên Suricata rule. Kích hợp một hành động bypass luồng dữ liệu trong phần cứng là việc đơn giản biên dịch Suricata với Napatech và bao gồm từ khóa bypass ở trong rule.

Một khi Suricata xác định được luồng dữ liệu đó sẽ được bỏ qua, mọi gói tin từ luồng đó sẽ được xử lý trong phần cứng của SmartNIC. Điều này giải pháp CPU khỏi nhiệm vụ xử lý gói tin, cho phép ứng dụng đạt được mức thông lượng cao hơn.

Trình diễn khả năng bypass phần cứng

Để thể hiện giá trị của việc bypass bằng phần cứng, phép thử sau đây sẽ so sánh thông lượng của Suricata trên một card mạng NIC tiêu chuẩn sử dụng phần mềm bypass với một hệ thống tương tự nhưng sử dụng Napatech SmartNIC với cơ chế bypass zero-copy packet DMA bằng phần cứng.

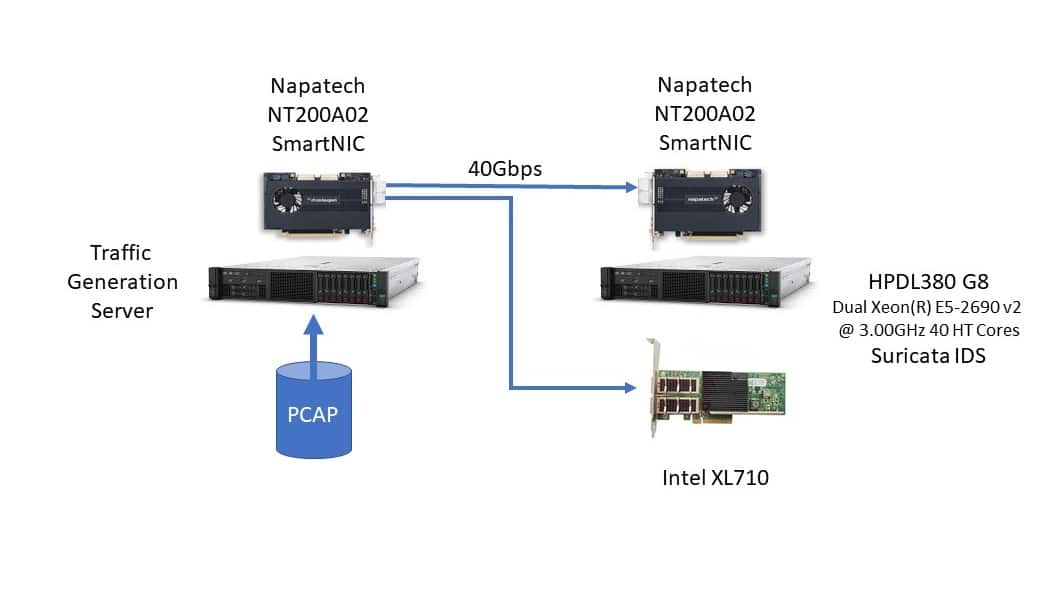

Cấu hình phần cứng

Cấu hình phần cứng sử dụng để kiểm thử dựa trên máy chủ dual-socket HP DL380 G8 với Intel® Xeon® E5-2690 v2 3.0 GHz CPUs (40 HT cores), chạy CentOS 7.5. Traffic được tạo ra từ PCAP replay của một traffic thực tế thu được bằng việc trộn gói tin TCP (88%) và UDP (12%) trong một triệu luồng dữ liệu duy nhất. Traffic này hoàn toàn tương tự với traffic ghi nhận được trong một môi trường doanh nghiệp lớn với hàng trăm người dùng sử dụng hàng tá các ứng dụng client-server cũng như truy cập internet.

Traffic được tạo ra bởi một ứng dụng Napatech PCAP replay trên một NT200 2x40GE SmartNIC và gửi đi trên đường kết nối 40 GE tới thiết bị cần kiểm thử device under test (DUT) sử dụng hoặc là Napatech NT200 SmartNIC (2x40GE) hoặc một Intel XL710 (1x40GE) network interface card.

Hình 1: Cấu hình kiểm thử

Cấu hình Suricata

Mọi tổ chức gần như phải luôn hiệu chỉnh bộ IDS/IPS của họ để có thể nhận ra đâu là các traffic thông thường trên mạng giống như việc so sánh nó với các hành động tấn công có chủ ý. Sự hiệu chỉnh này chính là thiết lập các quy ước rule và cho phép bypass một cách phù hợp. Với Suricata, việc bypass được thực hiện bằng từ khóa bypass trong các rule. Ở trong phép thử này, một rule đơn lẻ bype được tạo ra. Cấu trúc rule như sau:

drop tcp any [!80,!20,!21,!23,!25,!53,!67,! 68] <> any any (msg: “SURICATA Test rule”; priority:1;classtype:protocol-command-decode; bypass; sid:1000001; rev:2;)

Cụ thể, trong rule này, mọi traffic TCP sẽ được đi qua từ những traffice tới/từ một tập các cổng xác định. Ví dụ về rule tương tự cũng có thể được sử dụng cho traffice UDP.

Với các mẫu traffic trong phép thử này, khoảng 70% được đi qua trong khi 30% còn lại được xử lý hoàn toàn bằng phần mềm Suricata trên host CPU. SmartNIC vẫn cung cấp tính năng zero-copy DMA cho ứng dụng trong trường hợp này, nhưng mọi luồng dữ liệu đều phải được giải mã decode, đóng gói lại và được xử lý toàn bộ trong phần mềm.

Trong một ứng dụng thực thi lượng traffic được đi qua có thể từ 0 tới 100% và nhiều hơn traffic sẽ được đẩy qua SmartNIC cho việc xử lý, đồng thời nâng cao năng lực của hệ thống.

Kết quả kiểm thử

Với một IDS/IPS, hiệu năng là một yêu cầu tuyệt đối cho việc đảm bảo khả năng bảo vệ. Kết quả kiểm thử cho thấy chỉ 3% gói tin bị mất có thể dẫn tới 10% các cảnh báo bị bỏ qua, một lượng nhỏ 0/4% gói tin bị mất sẽ gây ra tỉ lệ 10% lỗi giải mã tập tin.

Trong phép thử này, thông lượng được bảo toàn bởi phần cứng bypass trên Napatech SmartNIC cao hơn 2.5 lần so với hệ thống sử dụng NIC tiêu chuẩn bằng phần mềm.

Thông lượng đo được trên Suricata:

- IPS sử dụng Emerging Threats Open Ruleset khi không có bypass: 15 Gbps

- IPS sử dụng Emerging Threats Open Ruleset với phần mềm: 30 Gbps

- IPS sử dụng Emerging Threats Open Ruleset với SmartNIC hardware bypass: 76 Gbps

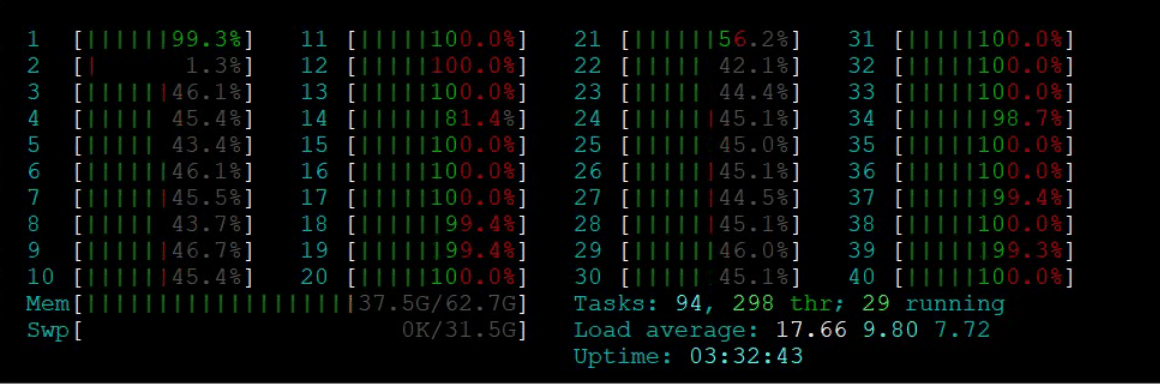

Tận dụng CPU

Trên cấu hình sử dụng NIC tiêu chuẩn, Suricata workload was very unevenly distributed, with roughly half the cores running at 100% utilization while others were at less than 50% utilization. The reason for this is that many other solutions exhibit asymmetric traffic distribution or exact a performance penalty for non-local memory access.

Hình 2: CPU utilization (standard NIC)

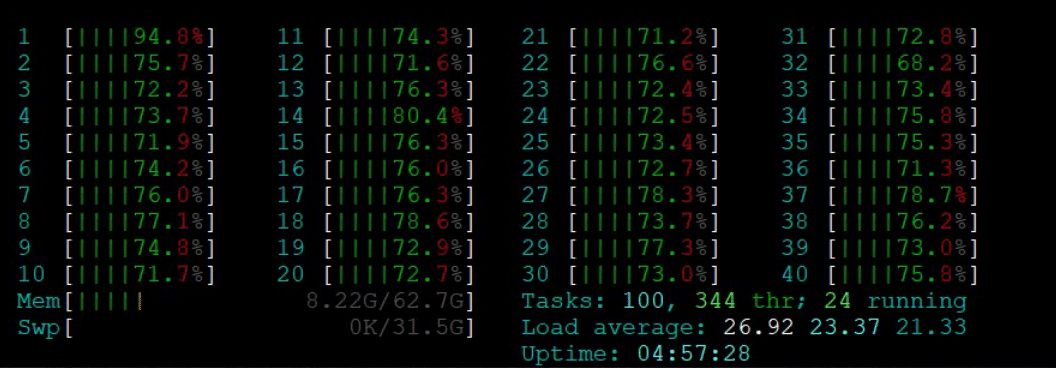

On the Napatech SmartNIC, the workload was much more evenly distributed across all cores, with essentially all cores loaded at less than 80%.

Hình 3: CPU Utilization (Napatech SmartNIC)

Kết luận

Phép thử này thể hiện khả năng xử lý của Suricata ở mức 76 Gbps mà không làm mất mát dữ liệu bằng cách đẩy dữ liệu qua Napatech FPGA-based SmartNIC. Trong phép thử tương tự không sử dụng Napatech, con số này là 30 Gbps thông lượng. Hơn nữa, phép thử với Napatech chứng minh rằng hệ thống hoạt động cân bằng, tận dụng được năng lực xử lý của CPU.

Thông số kỹ thuật

SmartNIC Hardware Feature Highlights

| General Hardware Specs | NT200A02 | NT50B01 |

| Dimensions | 1⁄2-length, full-height PCIe | 1⁄2-length, 1⁄2-height PCIe |

| Network Ports | 2×QSFP28 | 2xSFP28 |

| Data rate | 8×10Gbps,2×10/25Gbps, 4×10/25Gbps,2×40Gbps, 2×100Gbps | 2×10/25 Gbps |

| Onboard memory | 12GB | 10 GB |

| PCIe configuration | 16-lane 8 GT/s PCIe Gen3 | 16-lane 8 GT/s PCIe Gen3 |

Shared Hardware Feature Highlights

• Zero packet loss for all frame sizes from 64 bytes to 10,000 bytes

• keep or discard errored frames

• Addressing up to 1 TB application buffer memory

• Packet or segment delivery to the application

• Hardware-acceleration for:

• Multi-port packet merge

• Load distribution across up to 128 CPU cores

• Filtering based on e.g. L3/L4 criteria

• Stateful flow management

• GTP, IP-in-IP, GRE and NVGRE tunnel support

• IP fragment handling

• Slicing at fixed or dynamic offset

• De-duplication in hardware

• RMON1 counters, including jumbo frames

• IEEE 1588-2008 PTP and PPS time synchronization

• Hardware Time Stamp: Resolution: 1 ns

• Stratum 3 compliant TCXO

• OS time synchronization

Napatech Software Suite Feature Highlights

• NTAPI: Common API for all Napatech SmartNICs

• Simple programming interface allowing fast integration

• Zero copy transfer of data to host

• Zero copy transfer of data between SmartNICs

• Packet-based interface providing an abstraction of hardware details

• Stateful Flow-aware match and action processing

• Matching – flows are completely configurable based on the flexible key matcher

• Actions

• Drop (Block) – Drop unwanted traffic, reducing system resource reduction and increasing performance

• Forward (cut-through/bypass) – Local, on card, port to port forwarding, reduces CPU demands and PCIe bottlenecks, lowers latency to increase application performance

• Flow-based Load Balancing (RSS) – efficient and distributed CPU utilization

• Per-flow statistics (packets/bytes) with directional state per packet

• Flow Aging – Monitor TCP flow state, configurable timers for UDP

• Flow Metadata – information sharing between host application and SmartNIC offload engine

• Advanced features including:

• Data merging of port data from multiple SmartNICs into a single data stream

• Data sharing of captured data between multiple customer applications without the need for replication

• Operating systems: Linux, Windows

• ibpcap, WinPcap, and DPDK

• IEEE 1588-2008 PTP stack

• SDK tools included in source code for debugging and prototyping and as application examples

Pacotech phân phối các sản phẩm và giải pháp của Napatech tại Việt Nam. Vui lòng liên hệ để biết thêm chi tiết.

Nâng cấp Suricata với Napatech SmartNICs